Get Complete Project Material File(s) Now! »

From CMOS Image Sensor to Column-parallel ADC

The first devices with CMOS image sensor (CIS) technology on the market for the public use raised in 1990s. Despite of its low image quality in early years, CIS technology survived in the game thanks to following facts: capability to integrate peripheral functional circuit on the same die as the image sensor; less size and lower power consumption. In a past few decades, CIS technology has significant improvement by overcoming these draw-backs: increased noise and reduced sensitivity which makes them offer picture quality that meets or exceeds the capabilities of Charge-coupled devices (CCDs) [1]. Today CISs are suitable for many consumer domains (we-bcams, cell phones, digital cameras…). Fig. 1.2[2] shows a classical CMOS active pixel sensor (APS) architecture. An APS consists of 4 main parts: active pixel array, analog signal proces-sors, analog-to-digital converter (ADC) and peripheral logic control circuits. The active pixels are responsible for converting the number of photons into a voltage, via photodiodes. Analog Sig-nal Processors perform functions such as charge integration, gain sample and hold, correlated double sampling (CDS) and FPN suppression [3]. ADCs, as the name, convert analog signals to digital so that they can be used for the following signal processing.

After market revolution at the beginning of 2000, HD (high definition) is becoming the standard all around the world which means increased number of pixels in image sensor and decreased pixel array readout speed. To ensure frame rate, single ADC covering all pixels should work in very high speed which results in undesirably high power consumption. In order to release the constraint of ADC conversion frequency, the column-parallel ADC architecture was proposed.

Amount the existing column-parallel ADC dedicated to CMOS image sensor, single-slope ADC (SS ADC) are friendly in size. [4][5] provide a conversion rate higher than 100 kS/s and a maximum resolution of 10-11 bits. [6] Uses hybrid column counters and achieves 12 bits. Although it is possible to modify to the ADC in [6] in order to get higher resolution, the clock frequency of the counter in the ADC should be very high. Cyclic ADCs [7][8] which are compatible in size can achieve 12 to 13 bits resolution and operate faster. However highly requiring of components linearity makes it hardly achieve more. SAR ADCs provide low power consumption and a relatively high speed compared to other ADCs. However requiring of large area caused by capacitors in DAC decreases the compatibility with the size of pixel pitch. With a segmented capacitor DAC, [9]and[10], of which sizes are adapted to widths of their pixels, and achieve 12-bit resolution. Over-sampling ADC, such as sigma-delta ( ) ADC has been investigated for CMOS image because it requires relatively low precision analog components and reduces input temporal noise, compared to conventional Nyquist-rate converters. Although S/H module is suppressed, ADC works as incremental (I ) ADC in image sensor application for the reason that modulator is reset before every conversion beginning. Column-parallel ADC in [11] compatible with pixel pitch by using invertor-based amplifier[12] instead of operational amplifier, achieves 12-bit resolution and 220-kS/s conversion rate. It’s possible to obtain higher resolution by doubling the conversion time in theory. Also using invertor-based amplifier, [13] has 14-bit resolution and 100-kS/s conversion rate with the width of 70 m. The summary of different type column-parallel ADCs are shown in Table 1.1.

Challenge of ADC in the Earth Observation Application

Featuring significant advantages over CCD sensors (lower power consumption, integration mono-lithic…), CMOS technology is also expanding in some high-end space applications, such as the Earth observation which requires high-resolution, medium-speed as well as high-dynamic-range image sensors. [27] developed a 750 750 pixels CIS specifically designed in order to fit star trackers. Nowadays we use a full HD CIS with 1080 1920 pixels and 100-frame/s date rate to increase resolution and speed. Therefore, the ADC conversion rate should not be lower than 100 kS/s to allow CIS reading out 100 images per seconds. To guarantee high dynamic range, we challenge to design a column-parallel ADC with high resolution of effective 14 bits. To release the constraint of the ADC width, we place half of column-parallel ADCs at the top of pixel array and half of them at the bottom, as the CIS architecture shown in Fig. 1.5. However the width of each ADC still should not exceed the width of two pixels.

Pieretta: Chip of New Proposed Two-step I ADCs

Pieretta[28] is our response to the challenge. It is the name of the chip of two-step I col-umn ADCs. This ADC architecture was proposed by a previous PhD student Pierre Bisiaux who defensed in 2016.

Acting as a Nyquist rate converter, I ADC is an ideal candidate for medium-frequency and high-resolution application. Different from which focus on the output’s spectral properties, I ADC provides an accurate estimation for every individual sample. What’s more, because of its memory-less conversion, it can be easily switched between different signal sources. These characters make it suitable for image sensor applications. For this reason, Pierre decided to develop the ADC based on I ADC.

Conversion rate was an important consideration when the architecture of I ADC (modu-lator) was chosen. The use of 2nd order modulator provides a good trade-off between the number of clock cycles needed for a conversion and the circuit complexity. Once the order of the I modulator has been chosen, he found out the modulator input range based on Fig. 1.6 so that the quantization errors stay in a reasonable zone as the effective number of bits depends on the range of quantization errors. Fig. 1.7 shows the quantization errors in the function of the input of the I modulator when 25 clock cycles (OSR) are applied. According to it, if the input amplitude is limited to 0:8 reference voltage (the value of full scale voltage equals to two times the value of reference voltage), the quantization errors coverge to a normal range. This conclusion is also valid for OSR = 50 and OSR = 100, as shown in Fig. 1.8.

By choosing a two-step conversion approach, we can further reduce the number of clock cycles without extra circuit. Mr.Bisiaux also optimized the coefficients of the integrators in the I modulator for two purposes: first, making the range of residue in of first step close to the range of the modulator input, in order to eliminate inter-step gain, second, minimizing the residue of the second step so that to minimize the conversion errors. As shown in Fig. 1.9, the distribution of the residue of the first step is more ”uniform” than that of the residue of the second step. Thus for our architecture, if the ADC operates at a 20 MHz system clock with 72 clock periods, it is possible to achieve a conversion rate of 250 KS/s with a resolution of 14 bits, which provides the same performance as a one-step ADC with 286 clock periods.

As a column ADC, in order to fit its width with the pixel pitch, inverter-based amplifiers are employed instead of operational amplifiers (OTAs). CMOS inverters have also been found in the literature as being used for realizing OTAs for ADCs, because of it simple structure and[12][29] [30]. For low power applications, to reduce the power consumption of inverter-based OTAs, they are operated at lower supply voltages[31][32]. It is namely class-C operation where the supply.

Researches on I ADC Reconstruction Filter

For an I ADC, the correction and calibration are usually implemented in the digital filter. Even though I ADCs and ADCs can share this non-ideal integrator model, so far there isn’t any calibration technique dedicated to I ADC while there are several researches on the I ADC digital reconstruction filters for the purpose of resolution improvement.

As an example in Fig. 2.19, applying a digital reconstruction filter whose order is higher than the order of analog modulator allows increasing resolution and the average accuracy, but the range of quantization error around zero remains the same[81]. As shown in Fig. 2.20 (b), com-pared to Fig. 2.20 (a), quantization errors applying higher order digital filter are more smooth except the peak around zero input. To eliminate this peak, we can inject a dither signal into the loop before quantizer as it prevents the oscillation of the integrator output. The quantization er-rors with dither signal are shown in Fig. 2.20 (c). Since it can be considered as a high frequency quantization noise, it will be filtered by modulator.

A sinc filter can provide the suppression of a periodic disturbing signal and it is advised to chose its order L as La + 1, where La is the order of the analog modulator[81]. However they are also only valid in ideal circuit.

For I ADCs, [82] proposes a digital decimation filter (whose transfer function in z domain is H(z)) which is able to minimize the sum of modulator input thermal noise and quantization error. By knowing modulator ST F and N T F with finite-length impulse response, this digital filter can be mathematically derived. The noise model of an I ADC can be abstracted as the model shown in Fig. 2.21. Since the incremental ADC is reset every M clock period, the final result of the nth conversion cycle can be calculated as follows: v(n) = [stf0(k) u(k)]M;n + [stf0(k) t(k)]M;n + [ntf0(k) q(k)]M;n (2.11).

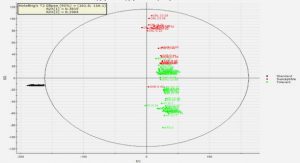

Parallel Simulations and Choice of the Modulator Input Values

We planned to test a set of inputs whose values varying between Vin;max, where Vin;max is the amplitude of the modulator input, in post-layout simulation. The number of samples should be sufficient large to ensure a stable estimation of ER, however, the post-layout simulation will take extremely long time for thousands of samples. We took two weeks for about 1500 samples in the post-layout simulation for one-step modes. In order to reduce the simulation time, we divided the whole simulation into four short simulations executed by different cores in parallel. And the input amplitude of each short simulations became 0:25Vin;max. To avoid overload of integrator, Vin;max was chosen as 0:8Vref .

It is simple to generate a set of ramp signals in the range of [VminVmas] with constant step. However, there is a great inconvenience performing simulations with this kind of signals: we cannot stop simulations at whenever we want. To solve this problem, we generated the input signals in each short simulation in a new way. Furthermore, the inputs are correlated and do not change very much between each value. This may hide some non-idealities issues that appear with large input steps.

N loops should be taken to generate all the inputs. During each loops, the input values are coded by a definitive number of binary bits. One bit is used for the inputs generated in the first loop so there are two different values in the input set. Then two bits are used for those generated in the second loop and after the second loop, two more inputs of different values are added to the input set. In each loop, we add 1-bit precision to code the input values and the length of the input set doubles. So in the last loop, the precision of the input is N bits. The diagram of inputs generation is shown in Fig. 3.17. Fig. 3.18 shows an example of the inputs generated with this method.

Post-layout Simulation of One-Step Conversion

In order to understand the circuit characteristics, we first make the ADC execute the one-step conversion. From equation (3.8), a 14-bit resolution is guaranteed by applying 286 clock cycles in one conversion. In practice, we chose 400 clock cycles with some margin. And finally there were 5600 input samples. According the simulation of an ideal modulator model on Matlab, the ER of the one-step conversion with 400 clock cycles is 15:4 bits, as shown in Fig. 3.19 (a).

Table of contents :

1 Introduction

1.1 From CMOS Image Sensor to Column-parallel ADC

1.2 Challenge of ADC in the Earth Observation Application

1.3 Pieretta: Chip of New Proposed Two-step I ADCs

1.4 Motivation and Problematic

1.5 Thesis Organization

2 State of the art

2.1 Incremental ADC

2.2 Linearization Techniques for ADCs

2.3 Researches on I ADC Reconstruction Filter

2.4 Conclusion

3 Two-Step I ADC and Circuit Pieretta

3.1 IADC Modeling

3.1.1 Second-Order I Modulator

3.1.2 Two-step conversion

3.1.3 Digital Reconstruction Filter

3.2 Design of I Modulator

3.2.1 Analog Circuit Part

3.2.2 Digital Circuit

3.3 Post-layout simulation results

3.3.1 Equivalent resolution

3.3.2 Parallel Simulations and Choice of the Modulator Input Values

3.3.3 Post-layout Simulation of One-Step Conversion

3.3.4 Post-layout Simulation of Two-Step Conversion

3.4 Conclusion

4 I ADC correction technique

4.1 Global error model

4.2 Correction methodology

4.3 State-of-the-art correction methods

4.3.1 Correction of gain and offset

4.3.2 Optimal filter

4.3.3 Correction results of existing methods

4.4 New proposed correction methods

4.4.1 Pattern-correcting filter

4.4.2 Correction results of pattern-correcting filter techniques applied to postlayout simulation

4.5 Corrections results for multi-step conversions

4.6 Correction method simplification

4.6.1 Simplified Filter

4.6.2 Hybrid filter

4.6.3 Simplified hybrid correction

4.7 Coefficient quantization

4.8 Resolution optimization for two-step conversion

4.9 Conclusion

5 Circuit defects modeling

5.1 Classical circuit non-idealities

5.1.1 Non-linear amplifier gain

5.1.2 Capacitor mismatch

5.1.3 Simulation of the modulator model with classic defects

5.2 New inverter-based SC integrator model with parasitic capacitors

5.2.1 Abnormal Variation of Certain Intern Signals in Integrators

5.2.2 Discovery of parasitic capacitors

5.2.3 Circuit-level models of integrators

5.3 Validation of the new proposed inverter-based SC integrator models

5.3.1 Parameters identification for the new proposed inverter-based SC integrator models

5.3.2 Comparison of the new proposed inverter-based SC integrator models to the ideal integrator model

5.4 Validation of the modulator model composed of the new proposed inverterbased SC integrator models

5.4.1 Parameters identification of other imperfections in modulator

5.4.2 Comparison of proposed modulator model and modulator in post-layout simulation

5.4.3 Study of the parasitic capacitor impacts on correction methods

5.4.4 Study of the noise resistance of correction methods

5.5 Further study on impact of parasitic capacitor to an inverter-based I modulator

5.5.1 Deduction of transfer function of the 2nd I modulator

5.5.2 Use of actual filter as the reconstruction filter for the non-ideal modulator .

5.5.3 Error analysis

5.6 Conclusion

6 Measurement

6.1 Package of Pieretta

6.2 Equipment of Test-bench

6.3 Asynchronous Sampling

6.4 Measurement Results

6.4.1 Interference of Noise and Primary Measurement Results

6.4.2 Filtered Measurement Results

6.5 Conclusion

7 Conclusion

A Study of Convergence in Parameter Estimation