(Downloads - 0)

For more info about our services contact : help@bestpfe.com

Table of contents

1 Introduction: Wake-Up Radios

1.1 Power Considerations in Wireless Sensor Networks

1.2 Wake-Up Receivers State of the Art

1.2.1 Architecture Considerations

1.2.2 Performance Analysis of Existing WU-RXs

1.3 Proposed WU-RX architecture

1.3.1 Proposed System

1.3.2 Low Power – Low Sensitivity WU-RX

1.3.3 High Sensitivity WU-RX

1.3.4 Interferer Resilient WU-RX

1.4 Tunable Filter Design

1.4.1 Continuous Time Analog Domain Filters

1.4.2 Discrete Time Charge Domain Filters

1.4.3 Digital Signal Processing

1.4.4 Continuous Time Digital Signal Processing

1.4.5 Tunable Filter Choice

1.5 Study of the Proposed CT Filtering Architecture

1.5.1 Single Tone Reception

1.5.2 Single Tone Reception with an Interferer

1.5.3 Single Tone Reception with Two Interferers

1.6 Wake-Up Receiver Design Conclusions

2 Continuous Time Processing Chain

2.1 Classification of the Different Signal Processing Domains

2.2 Description of the CT-DSP Chain

2.2.1 CT-ADC

2.2.2 CT-DSP

2.3 Co-Designing the CT-ADC with the CT-DSP

2.4 Proposed CT-ADC Architecture

2.4.1 Filtering CT-ADC Principle

2.4.2 Reducing the Input Event Rate

2.4.3 Effects on the Linearity of the Conversion

2.5 CT-ADC/DSP Conclusion

3 Energy Efficient CT-ADC

3.1 Previous Work

3.1.1 Basic Architectures

3.1.2 Improved Delta-Modulator Based CT-ADCs

3.2 Proposed CT-ADC

3.2.1 Improved Commutation Scheme

3.2.2 Proposed Architecture

3.2.3 Features

3.2.4 Possible Errors

3.3 Transistor-Level Implementation

3.3.1 Comparators

3.3.2 Transconductance

3.3.3 Threshold Management

3.3.4 Breakdown of the CT-ADC Power Consumption

3.4 Measurement Results

3.4.1 Single Tone Input: Noise

3.4.2 Two Tone Input: Linearity

3.5 CT-ADC Conclusion

4 Power Scalable CT-DSP

4.1 CT-DSP Architecture

4.1.1 Dual FIR – IIR Implementation

4.1.2 CT Digital Filter Design

4.1.3 Architecture Simulation

4.1.4 CT-DSP Specifications

4.2 CT Delay Cell

4.2.1 State of the Art for Asynchronous Delay Cells

4.2.2 Delay Cell Design

4.2.3 Delay Cell Architecture

4.2.4 Calibration and Matching

4.2.5 Delay Architecture Summary

4.3 CT Adder

4.3.1 Previous Work

4.3.2 Proposed Weighted-CT-Adder

4.3.3 Adder Performance

4.4 DF-CT-ADC

4.4.1 CT-ADC – CT-FIR Integration

4.4.2 Dispatcher

4.4.3 Voltage Gain and Filtering

4.4.4 Feedback Gm

4.5 Simulation/Measurements Results

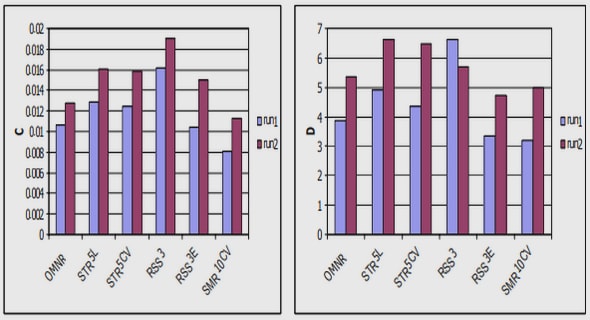

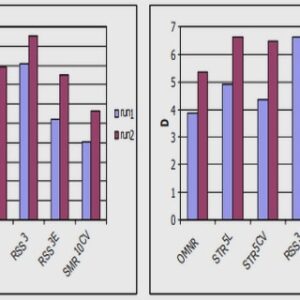

4.5.1 DF-CT-ADC Performance

4.5.2 CT-FIR Performance

4.5.3 Interferer Rejection

4.5.4 Power Consumption Scaling

4.5.5 Noise

4.5.6 Comparison with State of the Art

4.6 CT-DSP Conclusion

5 Conclusion

5.1 Motivations and Contributions of this Work

5.2 Improvements of the Proposed Design

5.2.1 CT-ADC

5.2.2 DF-CT-ADC Feedback Path

5.2.3 CT-DSP Delay Cells

5.3 Future Work