(Downloads - 0)

For more info about our services contact : help@bestpfe.com

Table of contents

1 Introduction

1.1 From CMOS Image Sensor to Column-parallel ADC

1.2 Challenge of ADC in the Earth Observation Application

1.3 Pieretta: Chip of New Proposed Two-step I ADCs

1.4 Motivation and Problematic

1.5 Thesis Organization

2 State of the art

2.1 Incremental ADC

2.2 Linearization Techniques for ADCs

2.3 Researches on I ADC Reconstruction Filter

2.4 Conclusion

3 Two-Step I ADC and Circuit Pieretta

3.1 IADC Modeling

3.1.1 Second-Order I Modulator

3.1.2 Two-step conversion

3.1.3 Digital Reconstruction Filter

3.2 Design of I Modulator

3.2.1 Analog Circuit Part

3.2.2 Digital Circuit

3.3 Post-layout simulation results

3.3.1 Equivalent resolution

3.3.2 Parallel Simulations and Choice of the Modulator Input Values

3.3.3 Post-layout Simulation of One-Step Conversion

3.3.4 Post-layout Simulation of Two-Step Conversion

3.4 Conclusion

4 I ADC correction technique

4.1 Global error model

4.2 Correction methodology

4.3 State-of-the-art correction methods

4.3.1 Correction of gain and offset

4.3.2 Optimal filter

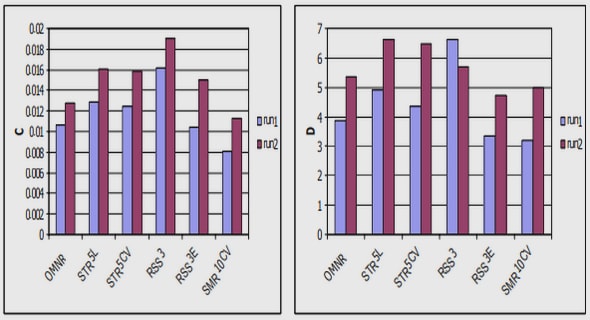

4.3.3 Correction results of existing methods

4.4 New proposed correction methods

4.4.1 Pattern-correcting filter

4.4.2 Correction results of pattern-correcting filter techniques applied to postlayout simulation

4.5 Corrections results for multi-step conversions

4.6 Correction method simplification

4.6.1 Simplified Filter

4.6.2 Hybrid filter

4.6.3 Simplified hybrid correction

4.7 Coefficient quantization

4.8 Resolution optimization for two-step conversion

4.9 Conclusion

5 Circuit defects modeling

5.1 Classical circuit non-idealities

5.1.1 Non-linear amplifier gain

5.1.2 Capacitor mismatch

5.1.3 Simulation of the modulator model with classic defects

5.2 New inverter-based SC integrator model with parasitic capacitors

5.2.1 Abnormal Variation of Certain Intern Signals in Integrators

5.2.2 Discovery of parasitic capacitors

5.2.3 Circuit-level models of integrators

5.3 Validation of the new proposed inverter-based SC integrator models

5.3.1 Parameters identification for the new proposed inverter-based SC integrator models

5.3.2 Comparison of the new proposed inverter-based SC integrator models to the ideal integrator model

5.4 Validation of the modulator model composed of the new proposed inverterbased SC integrator models

5.4.1 Parameters identification of other imperfections in modulator

5.4.2 Comparison of proposed modulator model and modulator in post-layout simulation

5.4.3 Study of the parasitic capacitor impacts on correction methods

5.4.4 Study of the noise resistance of correction methods

5.5 Further study on impact of parasitic capacitor to an inverter-based I modulator

5.5.1 Deduction of transfer function of the 2nd I modulator

5.5.2 Use of actual filter as the reconstruction filter for the non-ideal modulator .

5.5.3 Error analysis

5.6 Conclusion

6 Measurement

6.1 Package of Pieretta

6.2 Equipment of Test-bench

6.3 Asynchronous Sampling

6.4 Measurement Results

6.4.1 Interference of Noise and Primary Measurement Results

6.4.2 Filtered Measurement Results

6.5 Conclusion

7 Conclusion

A Study of Convergence in Parameter Estimation