(Downloads - 0)

For more info about our services contact : help@bestpfe.com

Table of contents

1 Introduction

1.1 Area of focus

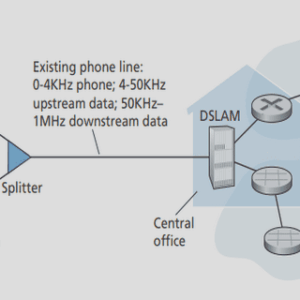

1.1.1 Problem of clocking in large digital circuits

1.2 Environment of the PhD project: the starting point and motivations

1.2.1 Network of coupled PLLs for clocking: history of the concept

1.2.2 Digital phase synthesis

1.2.3 Presentation of an ADPLL network prototype designed at LIP6 prior to my PhD thesis

1.2.4 Phase frequency detector (PFD)

1.2.5 Digital loop control of ADPLL network node

1.2.6 Digitally controlled oscillator (DCO)

1.2.7 Modeling of ADPLL and of ADPLL network

1.2.8 Stability of the PLL networks

1.2.9 Multiplicity of synchronization modes

1.2.10 Discussion of test results of the implemented prototype

1.3 Original contribution of my PhD project

1.4 Thesis outline

2 Network of distributed ADPLLs

2.1 Introduction

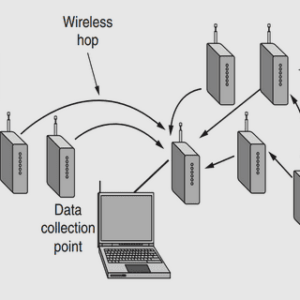

2.2 The architecture of clocking network proposed in this PhD project

2.3 Impact of quantization in ADPLL on its operation in steady state

2.3.1 Step 1: Impact of PFD and DCO quantization steps on the residual error

2.3.2 Step 2: impact of rounding in digital filter on the correction of residual phase error

2.3.3 Step 3: validation of block parameters by transient simulations

2.4 Specification of the network

2.5 Conclusion

3 ADPLL blocks design

3.1 Phase frequency detector (PFD)

3.1.1 The digital PFD architecture

3.1.2 Improvement of time-to-digital converter

3.1.3 Implementation of PFD

3.2 Digital filter in the ADPLL network

3.2.1 Architecture of digital filter

3.2.2 Implementation of the filter

3.3 Digitally controlled oscillator (DCO)

3.3.1 DCO Architecture

3.3.2 Control algorithm

3.3.3 Implementation

3.3.4 Serial programming interface (SPI)

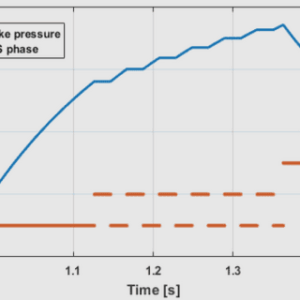

3.3.5 Simulation results

3.4 Conclusion

4 Built-In Clock Error Characterization Circuit

4.1 Introduction

4.2 State of art

4.3 Test methodology

4.3.1 Measurement theory

4.3.2 Architecture of measurement circuit

4.4 Low frequency discrete circuit prototype

4.5 High frequency on-chip prototype

4.5.1 Voltage-controlled delay (VCD)

4.5.2 Physical design of test circuit on silicon

4.5.3 Modeling of clock generator for system verification

4.5.4 Simulation results

4.6 Procedure of measurement

4.7 Conclusion

5 Clock network FPGA prototyping

5.1 Introduction

5.2 Implementation of FPGA based blocks

5.2.1 Synthesizable DCO

5.2.2 Synthesizable TDC

5.3 Experimental results

5.3.1 Stability and prevention of mode-lock

5.3.2 Phase error between two remote local clocks

5.4 Conclusion

6 Clock network silicon implementation

6.1 Introduction

6.2 Methodology of chip design

6.3 Implementation of local clock generator (NODE)

6.4 Floorplan of the chip

6.5 Design for test(DFT)

6.5.1 Chip programming

6.5.2 Built-in test circuits placement

6.5.3 Definition of the input/outputs of the chip

6.6 Chip layout

6.7 Simulation results

6.8 Conclusion

7 « Swimming pool »-like distributed architecture

7.1 Introduction

7.2 Modeling of infinite ADPLL network by a continuous wave propagation medium

7.2.1 From a discrete network to a continuous medium

7.2.2 An analogy with damped wave equation

7.3 ADPLL network with limited surface

7.4 Simulation results

7.5 Conclusion

8 ADPLL with sliding-window for wide range frequency tracking

8.1 Introduction

8.2 State of art

8.3 « Sliding window » architecture

8.3.1 Reference frequency indicator (RFI)

8.3.2 Coarse frequency adjustment

8.3.3 Phase error correction

8.4 Comparison with conventional PLL

8.4.1 Functional Simulation results

8.4.2 Power consumption comparison

8.5 Clock distribution network using « sliding window » ADPLL

8.5.1 Network structure

8.5.2 Evaluation of functional performance of system

8.6 Conclusion

9 Conclusion and Perspectives

9.1 Thesis summary and conclusions

9.2 Future work

9.2.1 Modelling of ADPLL for the study of residual phase error in steady state

9.2.2 Exploration of fault-tolerance property

9.2.3 Clock distribution for 3-D chip

Appendices

A VHDL models of the ADPLL blocks

B VHDL models for built-in test circuit

C Matlab scripts

D FPGA prototyping of the clocking network

E Tcl script for automatic floorplan of network

Bibliography