(Downloads - 0)

For more info about our services contact : help@bestpfe.com

Table of contents

1 Topology exploration

1.1 State of the art

1.1.1 Existing solutions for HVLP converters

1.1.2 Limitations of the Flyback topology

1.2 Topology exploration

1.2.1 Selected criteria

1.2.2 Input-Series Converters

1.2.3 Switched-Capacitor stages

1.2.4 Hybrid topologies: Multi-Level Flying-Capacitor converter

1.2.5 Comparison and selection of a candidate topology

1.3 Conclusion

2 Topology analysis

2.1 General approach

2.2 Analysis of the 2-level AHBF topology

2.2.1 Analysis of a switching period in steady-state

2.2.2 Important characteristics of the 2L-AHBF in low-power mode

2.3 Analysis of the 3L-FC-AHBF topology

2.3.1 Circuit analysis in steady-state

2.3.2 Outcomes of the switching period analysis

2.3.3 Early results from a discrete prototype

2.4 Conclusion

3 Design of an IC brick

3.1 Motivation and objectives of the IC design

3.2 Process limitations and proposed solution

3.3 Design overview

3.3.1 Power MOSFET

3.3.2 Gate-driver

3.3.3 Level-shifters

3.3.4 Active bootstrap

3.4 Conclusions on the design of the IC brick

4 Design of a transformer for HVLP converters

4.1 Selected approach for the transformer design

4.1.1 Introduction to the selected approach: Design of Experiments

4.1.2 Technological choices

4.1.3 Description of a simple model of the converter

4.2 Influence of the main design parameters

4.2.1 Example of a planar transformer design

4.2.2 Optimization of the primary inductance value in ZVS mode

4.2.3 Selection of the transformer turns ratio

4.2.4 Number of turns and balancing with frequency

4.2.5 PCB layers arrangement: mitigation of parasitic capacitors

4.2.6 Core size

4.2.7 Core material

4.3 Summary of the selected designs

4.3.1 Identifying the different types of design

4.3.2 Map of the Design of Experiments

4.4 Conclusion

5 Experimental measurements

5.1 Tests setup

5.1.1 Main board

5.2 Functional results

5.2.1 2L-AHBF configuration

5.2.2 3L-FC-AHBF configuration

5.3 ZVS mechanism and frequency optimization

5.3.1 Currents and parasitic capacitors

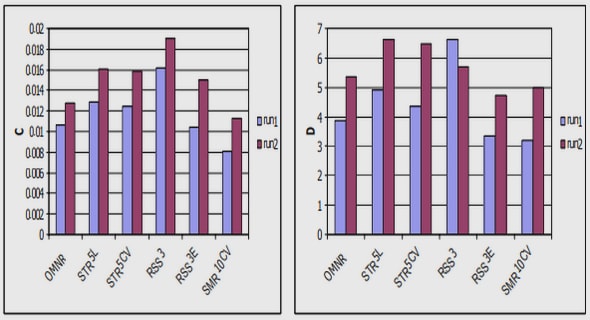

5.3.2 Optimization of the switching frequency

5.4 Transformer designs

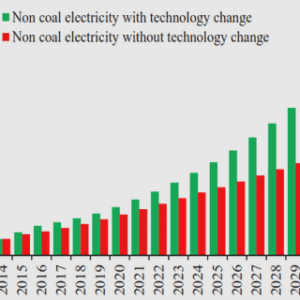

5.4.1 Core material

5.4.2 Number of turns

5.4.3 Core size

5.4.4 Winding arrangement

5.4.5 Conclusion on the transformer designs

5.5 Converter performances

5.5.1 Overall results

5.5.2 Losses at high frequency

5.5.3 Comparison with state-of-art