(Downloads - 0)

For more info about our services contact : help@bestpfe.com

Table of contents

1 Introduction

2 Multicore architectures

2.1 Overview

2.2 Hardware threads

2.3 Communication between hardware threads

2.3.1 CPU caches

2.3.1.1 Overview

2.3.1.2 Cache-coherent architectures

2.3.1.2.a Cache-coherence protocol

2.3.1.2.b Instructions used for synchronization

2.3.1.2.c Bottlenecks

2.3.1.3 Non-cache-coherent architectures

2.3.2 NUMA architectures

2.4 Hetereogeneous architectures

2.5 Machines used in the evaluation

2.5.1 Magnycours-48

2.5.2 Niagara2-128

2.5.3 Performance comparison

2.5.3.1 Cache access latencies

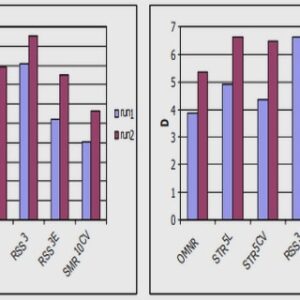

2.5.3.2 Contention overhead

2.5.3.3 Application performance

2.5.3.4 Summary

2.6 Conclusion

3 Lock algorithms

3.1 Blocking locks

3.2 Basic spinlock

3.3 CLH

3.4 MCS

3.5 Time-published locks

3.6 Oyama

3.7 Flat Combining

3.8 CC-Synch and DSM-Synch

3.9 Comparison of lock algorithms

3.10 Other lock algorithms

3.11 Conclusion

4 Contribution

4.1 Remote Core Lock

4.1.1 Core algorithm

4.1.2 Implementation of the RCL Runtime

4.1.2.1 Ensuring liveness and responsiveness

4.1.2.2 Algorithm details

4.1.3 Comparison with other locks

4.2 Tools

4.2.1 Profiler

4.2.2 Reengineering legacy applications

4.3 Conclusion

5 Evaluation

5.1 Liblock

5.2 Microbenchmark

5.3 Applications

5.3.1 Profiling

5.3.2 Performance overview

5.3.3 Performance of SPLASH-2 and Phoenix applications

5.3.4 Performance of Memcached

5.3.5 Performance of Berkeley DB with TpccOverBkDb

5.3.5.1 Experimental setup

5.3.5.2 Performance analysis

5.3.5.3 Yielding the processor in busy-wait loops

5.4 Conclusion

6 Conclusion

A French summary of the thesis

A.1 Introduction

A.2 Contribution

A.2.1 Algorithme de RCL

A.2.2 Outils

A.3 Évaluation

A.3.1 Microbenchmark

A.3.2 Applications

A.4 Conclusion