(Downloads - 0)

For more info about our services contact : help@bestpfe.com

Table of contents

Remerciements

Résumé

Abstract

1 Introduction

1.1 Thesis motivation

1.1.1 The advent of many-cores

1.1.2 The advent of Networks-on-Chips

1.1.3 Many-cores for hard real-time applications

1.1.4 Mapping applications onto NoC-based many-cores

1.2 Thesis contributions

1.2.1 The DSPINpro programmable Network-on-Chip

1.2.2 The Automatic real-time mapping and code generation

1.2.3 An environment for virtual prototyping of MPPA applications

1.3 Outline

2 State of the art

2.1 Network-on-Chip design

2.1.1 NoC building blocks

2.1.2 NoC topology

2.1.3 NoC switching

2.1.3.1 Routing

2.1.3.2 Switching method and buffering policy

2.1.3.3 Arbitration/Scheduling

2.1.4 Existing Network-on-Chip architectures

2.1.4.1 DSPIN

2.1.4.2 Æthereal

2.1.4.3 Nostrum

2.1.4.4 Kalray MPPA NoC

2.1.4.5 The scalar interconnect of MIT RAW

2.1.4.6 Other NoC architectures

2.1.4.7 Comparison with our work

2.2 Massively parallel processor arrays

2.2.1 Tilera TILEPro64

2.2.2 Kalray MPPA-256

2.2.3 Adapteva Epiphany

2.2.4 Intel SCC

2.2.5 ST Microelectronics STHORM

2.2.6 TSAR

2.2.7 Academic MPSoC architectures with TDM-based NoC arbitration

2.3 Static application mapping

2.3.1 Off-line real-time multi-processor scheduling

2.3.1.1 The AAA/SynDEx methodology

2.3.2 The StreamIt compiler for the MIT RAW architecture

2.3.3 Compilation of the SC language for the Kalray MPPA256 platform

2.3.4 Other mapping approaches

3 Tiled MPPA architectures in SoCLib

3.1 MPPA structure

3.2 Memory organization

3.2.1 Distributed shared memory

3.2.2 Address structure

3.2.3 Global memory organization

3.2.4 Tile memory organization

3.2.5 Hardware/software interface

3.3 Improving the timing predictability of the SoCLib tile

3.4 SystemC simulation and compilation support

4 Programmable NoC arbitration

4.1 The case for programmed arbitration

4.1.1 The principle

4.1.2 Target application classes

4.1.3 The cost of programmability

4.2 Programmable DSPIN

4.2.1 NoC router extensions

4.2.2 Area overhead

4.3 A simple example in depth

4.4 Case study: the FFT

4.4.1 FFT algorithm description

4.4.1.1 Mapping onto the MPPA architecture

4.4.1.2 Traffic injection configuration

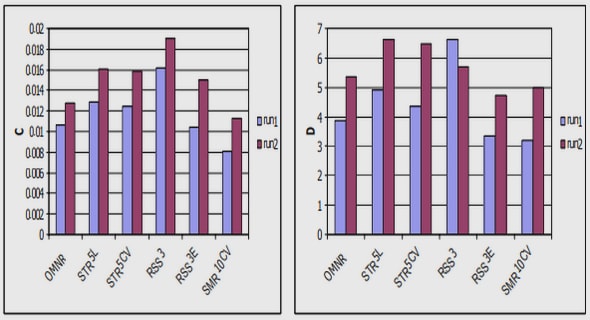

4.4.2 Evaluation of the slow-down due to traffic injection

4.4.3 Removing the slow-down through NoC programming

5 Off-line mapping of real-time applications using LoPhT

5.1 Background: AAA using the Clocked Graphs formalism

5.1.1 The Clocked Graph formalism

5.1.1.1 Functional specification

Clocks

Clocked graphs

Example

Support of a clock

Well-formed properties

5.1.1.2 Non-functional specification

Platform model

Non-functional properties

5.1.2 Off-line scheduling of CG specifications

5.1.2.1 Scheduled clocked graphs

5.1.2.2 Real-time scheduling problem

5.1.2.3 Consistency of a scheduled clocked graph

Notations

Consistency properties

5.1.2.4 Makespan-optimizing scheduling algorithm

5.2 Static (off-line) mapping onto MPPA architectures

5.2.1 AAA for NoC-based MPPA: The problem

Limitations

5.2.2 Extension of the CG format

5.2.2.1 Modeling of MPPA resources

NoC ressources:

Tile ressources:

5.2.2.2 Memory footprint specification

5.2.2.3 Non-functional properties

Worst-case computation durations

Worst-case communication durations

5.2.3 Makespan-optimizing scheduling

5.2.3.1 Mapping NoC communications

5.2.3.2 Multiple reservations

5.3 Automatic code generation

5.3.1 Tile code generation

5.4 Experimental results

Conclusion

List of Publications

Bibliography