Get Complete Project Material File(s) Now! »

Proposed Energy Harvesting Circuit

Some design specification criteria should be justified for proposed energy harvesting circuit for indoor solar applications based on the ambient environment and circuit requirements. First, the circuit should sustain long lifecycle. In another word, even the environment is completely dark, there should be power source to support load to working properly. Second, the circuit should take different kind of PV panels, means that the input voltage/power range should be as large as possible. Third, the maximum power tacking strategy should be power efficient and possibly have good compromise of certain accuracy and large search window. Lastly, the power management circuit should be power efficient itself, any power-hungry circuit should be avoided to use.This chapter describes the detail design of the proposed power management circuit to achieve the specification criteria above. Section 3.1 describes the power stage circuit and explains the detailed operation and its control method. Section 3.2 illustrates the proposed MPPT strategy which is an improvement from the two common method introduced in the Section 2.2. Section 3.3 introduces some basic building blocks and the circuit operation is explained in detail.

Zero Current Detection

For buck-boost converter running in the DCM mode, after inductor has been discharged, the switches on the discharging path should be all turned off when inductor current touches zero. Otherwise, it cases energy leakage which waste of power. Zero current detection was found in many works, and one of the methods was adopted in this work [2, 14, 15, 17, 18]. The voltage Vsw1 in the Figure 3.1 is compared with ground or the drain and source voltage of M3 is compared by a clocked comparator. Wherever the drain/source voltage of M3 flips that’s the point where inductor touches zero. The waveform is shown in the Figure 3.3. Thus, in the Figure 3.4, if Vsw1 is larger than ground, the positive terminal of clocked comparator will generate a pulse which to trigger the discharging path switches to turn off. Also, turning off the oscillator and clocked comparator to save the power. This ZCD circuit can be re-initiate when the next ZCD need to be used.

Proposed MPPT method

In this section, the proposed MPPT method will be explained. Combining section 2.2, the pros and cons of each MPPT method will be analysis. The primary advantage of proposed MPPT method is fully digitalized, simple and one universal search window with certain accuracy and large search window.

Method Overview

In this proposed MPPT method, we used both perturb and observe (P&O) and fractional open-circuit (FOCV) method. The flowchart of this algorithm is shown in the Figure 3.5. Firstly, in the P&O mode, the circuit will sample the open-circuit voltage and start perturbing process. The perturbing parameter is usually either PV voltage directly or load impedance of PV panel indirectly. In this proposed design, we perturb percentage (ratio), k, respect to open-circuit voltage sampled. Observing process will be done by power measurement circuit. The next perturbing direction will be determined based on the power measurement circuit compared results. Until we find optimal ratio k, we will leave P&O mode, and entering periodical FOCV mode. Since the indoor solar environment is very stable, the illumination level won’t change much. The assumption is made here that optimal ratio k doesn’t shift significantly.

P&O Mode

The open-circuit voltage will be sampled based on the method described in [18]. The sampling circuit is shown in the Figure 3.6, where Ss is the sampling switch, S1, S3 are the switches in the power converter. CS/H is the sample/hold capacitor to store the open-circuit voltage. The value of sample/hold capacitor CS/H needs to be carefully picked by considering the leakage of capacitor charge and hold time. Starting from open-circuit voltage, the circuit will initiate the perturbing process. The perturb range in this design is set to be from 100% to 60% (if the open circuit is included). 5% interval between is the resolution. This can be achieved by using a 3-bit digital controlled reference ladder as shown in the Figure 3.7. VOCK <0:2> are 3 digital controlled bit and associated with 3 switches to either short the corresponding resistance R0-R3 respect. The resistance value is adjusted based one the binary order, for example, R1 = 2R0, R2 = 4R0. Rx and Ry divider network are used to set up the first search point at 95%.

FOCV Mode

After optimal ratio k is found, the circuit will enter periodic FOCV mode like in [18]. The block diagram for FOCV mode is shown in the Figure 3.11. As main switch is disconnected, the PV voltage will recover back the open-circuit voltage. The sampling switch will be closed to sample the open-circuit voltage in the S/H capacitor. This voltage reference is then sent to the reference ladder shown in the Figure 3.7. The sampling behavior waveform is shown in the Figure 3.12. Meanwhile, another feature to have back-up battery is that during sampling period, PV is disconnected from the load and no energy is transferred. Then battery will continuously deliver energy to the load. Thus, load power will not be interrupt comparing with typical FOCV method with single path architecture. Since the indoor environment doesn’t change much, so open-circuit voltage would not shift significantly. Thus, longer sampling period can be used, such as 16 or 32 seconds. Since the simulation tool such as Cadence in this design doesn’t suitable for running such long simulation. The clock to generate long sampling clock is intended to be off-chip and leave the freedom to external changes.

Simulation Results

The circuit was designed and simulated using Cadence 6.1.6 version with TSMC BCDMOS 180 nm process design kit (PDK). To fully verify the actual performance after IC is fabricated, the post layout simulation adding parasites effected is simulated and verified. The die photo of the proposed circuit and system is shown in the Figure 4.1. The entire IC is 1.5 mm by 1.5 mm with active area around 1 mm by 1mm. The core is supplied by 1.8 V and the analog I/O is supplied by 5 V.

Zero Current Detection

The zero current detection is shown in the Figure 4.3. The ZCD circuit clock frequency is running at 35 MHz which compromise the good accuracy and power dissipations. When on-time finished, the ZCD circuit will start by initiating oscillator. During ZCD operation, the positive input terminal, VSW1 is compared with GND continuously. Until VSW1 is larger than GND, the point is exactly where inductor current reach zero. The positive output Comp+ will generate a pulse to indicate the zero-crossing point is found. The corresponding control signal will then turn off discharging-path switches. The offset is verified below 10 mV. After switches turned off, the parasitic capacitors and inductor will form a LC oscillator circuit. That’s why the oscillation will be observed after all switches are turned off.

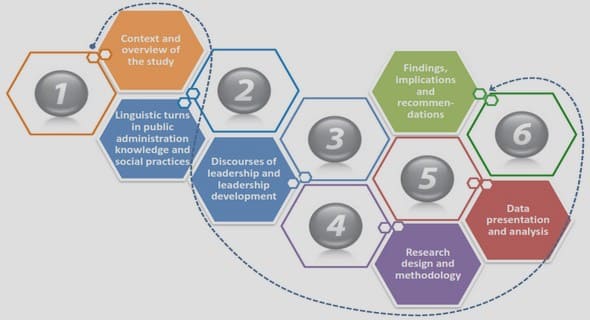

1. Introduction

1.1 Motivation

1.2 Scope of the Proposed Research

1.3 Proposed Approach and Technical Contribution

1.4 Organization of this Thesis

2. Preliminaries

2.1 PV Panel Characteristics and Modeling

2.2 Maximum Power Point Tracking Strategies

2.3 Power Converter Design

2.4 Impedance Matching

2.5 Previous Works

2.6 Chapter Summary

3. Proposed Energy Harvesting Circuit

3.1 Dual-input Dual-output Buck-boost Converter (DIDOBB)

3.2 Proposed MPPT method

4. Simulation Result

4.1 Capture Results

5. Conclusions

5.1 Key Contributions

5.2 Future Work

GET THE COMPLETE PROJECT

Energy Harvesting Circuit for Indoor Light based on the FOCV Method with an Adaptive Fraction Approach