Lumped Element Segmented MZM solution

The performance of an MZM is characterized by parameters such as analog bandwidth, voltage swing required for a _ phase shift (V_), and insertion loss [17]. Simultaneous achievement of low V_ and high bandwidth is crucial for low power operation at high data rates. Most of the existing SiP MZMs applied TW electrodes with continuous phase shifters [48]. High-speed optical modulation in silicon is typically achieved in reverse-biased p-n junctions embedded in optical waveguides. Due to the relatively weak electro-optic e_ect, a long optical phase shifter is required for a CMOS-compatible driving voltage, making high bandwidth challenging due to the RF losses along the p-n junction loaded electrodes and the velocity mismatch between RF driving signals and optical waves. In addition, a travelling-wave MZM (TW-MZM) requires 50 termination, which is power consuming. As a result of these limitations, it is di_cult to implement wide-band drivers using low power CMOS technologies for CMOS-SiP integrated transmitters.

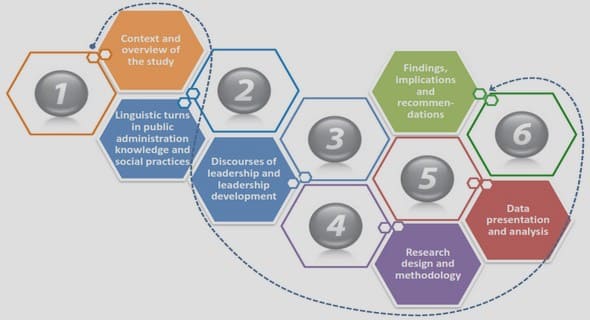

We examine lumped-element segmented MZM (LES-MZM) _rst investigated on InP [49], as shown in _gure 2.1. In this structure, each phase-shifter segment, including the electrode and p-n junction, can be treated as a lumped element in the desired frequency range. This approach overcomes the disadvantages of the TW-MZM. The velocity mismatch between RF and optical waves can be compensated by tunable delays between adjacent driving channels for a higher bandwidth. Therefore, a longer phase shifter, consisting of a sequence of lumped- element segments, can be implemented to reduce the driving voltage.

While PAM-4 modulation up to 56 Gb/s [19] (and more recently quadrature amplitude modulation [50]) was demonstrated using segmented MZMs with hybrid integrated CMOS drivers, these devices are based on a monolithic fabrication process or vertical carrier accu- mulation structure, requiring thin oxide gates and deposition of polycrystalline silicon (SIS- CAP), which are not widely accessible and are not compatible with other photonic components developed on popular 220-nm silicon-on-insulator (SOI) wafers. Depletion-mode optical modulators with lateral p-n junctions are widely available in SiP foundry processes. However, as previously discussed, TW-MZMs su_er from trade-o_ between bandwidth, voltage swing, and insertion loss [51]. Since generating very high voltage swings is not practical in sub-micron CMOS processes, optical modulators with lower V_ are desired.

Measurements and Discussion

The CMOS driver is fabricated in IBM 130 nm RF process. The entire die area of the driver is 1.5 mm2 (1 mm_1.5 mm). The photonic chip was fabricated at A*STAR’s IME, Singapore. A photo of the LES-MZM and its co-designed CMOS driver is shown in _gure 2.17. Wire bonding is used to connect the output of each channel in the CMOS driver to each segment of the MZM.

The operating point of the MZM is adjusted by means of DC bias voltage to achieve maximum eye opening (as a result, the bias point is slightly shifted from the quadrature point of the modulator). Driver Characterization Figure 2.18 shows the experimental setup used to test our chips. At _rst, the output of the driving channels are examined.

Figure 2.19 shows the output waveform of one of the driving channels, (the others show similar behaviours) while driving a 50 load. It shows a swing of 1.6 Vp?p at 20 Gbaud. The overshoots and jitters (5.4 ps) in the eye diagram are mainly from the inductance introduced by the wire bonds. Outputs of the three channels are shown in _gure 2.19, where _7 ps delay between two adjacent channels is obtained at 20 Gbaud. In the following, the programmable delay is examined. Figure 2.20 shows the measured results for the generated delay at di_erent frequencies.

The maximum and minimum delays generated from the _xed and tunable delay blocks are 14.5 ps and 10.6 ps, respectively, at 8 GHz. These values change to 12 ps and 7.2 ps, respectively, at 20 GHz. Tuning is achieved through three control bits (b0 , b1 , b2 ). While a maximal delay of 22.5 ps between two adjacent driving channel was expected at 20 Gbaud (when b0 =1) according to our simulation, only 12 ps was measured due to an unexpected issue in the coarse delay generation. We suspect this issue is related to a bug in the circuit implementation, resulting in failure to achieve the predicted value for the coarse delay (27.5 ps in __2 and 45 ps in __3) when b0 = 1. As shown in the simulation results presented in section 2.5, _gure 2.16, failure in applying the required delay between two adjacent segments causes skewed eye openings.

At high baud rates, these skewed eye opening causes sever increase in BER of the transmitter. Figure 2.20 shows that, for baud rates higher than 17 GHz, the maximum delay achieved is less than 13 ps, smaller than the optimal value (14 ps) predicted by simulation. Total power consumption of the driver was 375 mW for 38 Gb/s. The breakdown of power consumption of the driver is shown in _gure 2.21. The driver output stage consumes most of the power. CML bu_ers consume 30% of the total power. Power consumption decrease to 290 mW at 20 Gb/s.

SiP modulator model and operation

Traveling wave Mach-Zehnder modulators are the most promising candidates for commercial optical transmitters due to their thermal insensitivity and high tolerance to fabrication im- perfections as compared to micro-ring modulators. Although we focus here on TW-MZMs, the procedures we describe could be extended to apply to other modulators as well. Consider a typical traveling wave SiP Mach-Zehnder modulator that employs silicon waveguides with lateral p-n junctions.

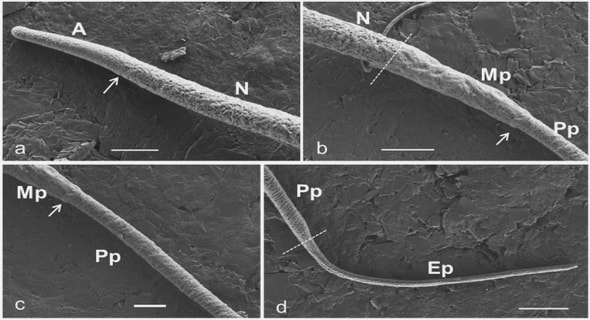

Figure 3.1 presents a schematic of a SiP TW-MZM driven in a series push-pull con_guration. A negative voltage is applied between the two arms of the MZM, and the traveling wave electrodes are terminated through a matched load. The cross section of the SiP MZM in a CMOS compatible SiP process on a 220-nm SOI wafer with 2 _m buried oxide (BOX) and lateral p-n junction (i.e., A_STAR’s IME, Singapore) is the same as the one presented in _gure 2.4 in the second chapter, section 2.3. We use the same procedure as the one presented in section 2.3 (_gure 2.2), to predict the electro-optic characteristics of the the phase shifter in Lumerical software. We use the same doping densities and wavelength of _ = 1550nm, unless otherwise noted. We _nd the change in e_ective index, _neff , in Lumerical as a function of applied reverse voltage. A plot of _neff is given in _gure 2.5b.

1 Introduction

1.1 Brief history of Silicon Photonics

1.2 Challenges in SiP integrated circuits

1.3 Modulating light in silicon.

1.4 CMOS-SiP transmitters

1.5 Thesis structure

2 CMOS-Photonics Co-design of an Integrated DAC-less PAM-4 Silicon Photonic Transmitter

2.1 Introduction

2.2 Overview of Design Strategy .

2.3 SiP Segmented Modulator Design .

2.4 CMOS Driver

2.5 Results of the CO-Simulation

2.6 Measurements and Discussion

2.7 Conclusion

3 Assessing Performance of Silicon Photonic Modulators for Pulse Am- plitude Modulation

3.1 Introduction .

3.2 SiP TW-MZM Modeling

3.3 MPP Including ISI

3.4 MPP and FOM

3.5 Discussion

3.6 Conclusion

4 Silicon Photonic In-phase and Quadrature-phase Modulators for 400 Gb/s and beyond

4.1 Introduction .

4.2 Design and Characterization of TW-MZM

4.3 Optimization for QAM

4.4 Experimental results

4.5 Conclusion

5 Conclusion and future works

A Appendix

A.1 E-O bandwidth: estimation

A.2 ISI e_ect with Gaussian response

A.3 FOM ISI term

Publication list

Bibliography