Get Complete Project Material File(s) Now! »

Methodologie´ d’extraction et modelisation´ du substrat

Dans ce qui suit, nous detaillons´ notre approche pour l’extraction post-layout incluant les parasites du substrat. Le flot de la figure 1 decrit´ l’idee´ gen´erale´.

Notre flot d’extraction se compose de 2 parties :

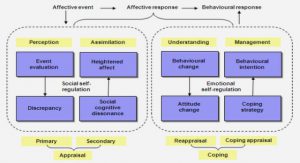

Extraction du reseau´ representant´ le comportement du substrat. Nous avons developp´e´ un moteur d’extraction en nous appuyant sur la base de donnees´ Open Access. Nous avons integr´e´ l’extracteur dans l’environnement de conception Cadence, parametr´e´ suivant la tech-nologie ams AG (en completant´ le Process Design Kit –PDK– de cette technologie). L’appro-che que nous suivons pour modeliser´ le substrat est illustree´ par la figure 2, et sera expliquee´ dans les paragraphes suivants.

Extraction des resistances´ et capacites´ (RC) et retro´-annotation de la netlist. Pour retro´-annoter la netlist post-layout standard du circuit principal avec le reseau´ modelisant´ le sub-strat, nous avons defini´ des terminaux supplementaires´ a` l’interface entre le substrat et le circuit principal dont les masques sont “au-dessus” du substrat. On utilise ces terminaux pour relier automatiquement, par des courts-circuits, les fils metalliques´ du circuit principal au reseau´ de composants parasites representant´ le substrat.

Figure 2: Modelisation´ d’une diode simple : approche pour l’extraction des parasites du substrat.

Notre methodologie´ suit 3 phases pour extraire le reseau´ de composants parasites representant´ le substrat :

La region´ que nous considerons´ pour l’extraction particuliere` du substrat se situe en dessous des zones de diffusion des transistors. Nous considerons´ d’une part les puits de diffusion : par exemple le puits profond N (DNTUB) et le puits profond P (DPTUB) du proced´e´ technologique ams AG 0.35µm HV-CMOS, et les implants : par exemple l’implant N (NDIFF) et l’implant P (PDIFF). D’autre part, nous considerons´ que tous les autres materiaux,´ comme les couches metalliques´ et les vias, ne produisent pas de composant parasite de substrat et nous les ignorons dans cette phase d’extraction. Nous utilisons des regles` specifiques´ pour definir´ les masques impliques´ pour un processus technologique cible. Les regles` sont exprimees´ en langage XML (Extensible Markup Language –XML–). Par consequent,´ dans notre approche, nous commenc¸ons notre processus d’extraction des composants parasites du substrat par une phase de definition´ d’un jeu reduit´ de masques, et la production d’une version reduite´ du layout par rapport a` sa version issue directement de la conception, sur laquelle nous procedons´ aux etapes´ suivantes :

Le maillage en volume du substrat s’appuie sur des el´ements´ localises´ en 3-D (i.e. cubes). Chaque el´ement´ represente´ une region´ differente´ du substrat et peut avoir une taille differente´. Pour con-struire le maillage en 3D, nous procedons´ en trois etapes:´ 1). definition´ des differents´ niveaux suivants l’axe vertical; 2). maillage en surface 2D; 3). optimisation du maillage 2D.

Niveaux suivants l’axe vertical : Pour effectuer le maillage, le substrat est divise´ en plusieurs couches, ou tranches, empilees´ selon la verticale. Le nombre total de tranches est cal-cule´ a` partir de l’epaisseur´ des puits suivant la profondeur des jonctions. Par exemple, si l’on considere` une region´ de substrat d’epaisseur´ de 20 µm, les couches consider´ees´ dans ce cas sont DNTUB et DPTUB (Figure 2(b)). Finalement, dans ce cas, le maillage ver-tical conduit a` considerer´ 3 tranches. La “coupe” a` travers la jonction PN (DNTUB vers substrat-P) et la “coupe” DPTUB vers le substrat de type P conduisent aux trois tranches suivantes : la tranche “haute” comprend les puits DPTUB et DNTUB et le substrat de type P (Figure 3b); la tranche “milieu” ne comprend que DNTUB et le substrat de type P (Fig-ure 3c); puis la tranche “basse” est composee´ uniquement du substrat de type P (figure 3d). Le tableau 2 presente´ les informations pertinentes pour le maillage, telles que l’epaisseur´ (deuxieme` colonne) des puits ou des implants (troisieme` colonne) a` chaque tranche con-sider´ee´ (indice dans la premiere` colonne). En outre, les zones de diffusion de type N et de type P sont consider´ees´ comme des contacts sur la surface de la tranche “haute” tranche (Figure 3a).

Maillage 2D en surface : une fois que le substrat est divise´ en tranches, on construit un maillage 2D sur la surface (axes x-y) au niveau de chaque tranche. Comme les puits ont differentes´ profondeurs de jonction, les maillages 2D sont differents´ d’une tranche a` l’autre (Cf. Fig-ure 3). Dans notre methodologie,´ le maillage le 2-D est base´ sur des points et non pas sur des formes pred´efinies´ (par exemple un rectangle ou un polygone est represent´e´ par une com-binaison de points ordonnes)´. Le coutˆ pour le calcul et la memoire´ utilisee´ augmentent a` mesure que le layout devient plus complexe. Avant de commencer a` construire le maillage, nous recueillons les sommets que nous sauvegardons comme :

ou` n est le nombre total de sommets relies,´ chacun representant´ un point, a` savoir v j = (x j; y j). Si un point 2-D peut decrire´ un emplacement sur la surface, alors deux points 2-D decrivent´ un segment correspondant a` une limite de jonction. L’extension de ce segment jusqu’aux extremit´es´ des bords devient une ligne du maillage (ligne noire sur la figure). L’ensemble des projections de ces sommets sur l’axe x est appele´ X array, et celui des pro-jections sur l’axe y, Yarray. Dans notre cas, ils sont exprimes´ par :

Figure 3: Maillage 2D pour chaque tranche: (b) “haute”, (c) “milieu”, (d) “basse”, et (a) Diffusion N+/P+ sur la surface du “haut”. fa1, a2,…gsont les coordonnees´ sur l’axe x, et fb1, b2, …g sont les coordonnees´ sur l’axe y. Les lignes en noir representent´ les lignes de maillage. Les lignes en rouge sont les fils metalliques´ dans la netlist. Les symboles en jaune et rouge representent´ respectivement des diodes DN-PS et des resistances´ dans le substrat-P.

ou` p est le nombre total de coordonnees´ sur l’axe x, et q celui sur l’axe y. Ces deux ensembles de points servent a` construire le systeme` de coordonnees´ du maillage resultant´. Pour chaque el´ement´ de maillage, sa profondeur est egale´ a` l’epaisseur´ de la tranche (Cf. Tableau 2) et sa surface est definie´ par les coins opposes,´ soit par le coin inferieur´ gauche (LL) et le coin superieur´ droit (UR). Finalement, la geom´etrie´ de l’el´ement´ peut etreˆ exprimee´ sous la forme :

Figure 4: Principe pour optimiser la tranche “haute”. Les points rouges dans la figure (b) representent´ les sommets des formes geom´etriques´ (la couche DPTUB est un polygone et la couche DNTUB est un rectangle).

Optimisation du maillage : Nous venons d’introduire une methodologie´ pour mailler le substrat. Cette methode´ repose sur un maillage 2D rectiligne du substrat. Nous avons present´e´ dans l’article [47], une strategie´ de maillage optimise,´ qui contribue a` reduire´ de fac¸on signi-ficative la taille du reseau´ maille,´ et ainsi accel´erer´ la simulation. Dans cette section, nous presentons´ cette strategie´ d’optimisation du maillage sur la tranche ”haute” de la structure, en ayant en teteˆ que cette strategie´ peut etreˆ appliquee´ a` chacune des tranches du maillage 3-D.

La strategie´ initiale de maillage (S1) est represent´ee´ sur la figure 4a. Dans notre approche, le maillage est construit par des cubes 3-D dont la hauteur est definie´ par la profondeur de la tranche, et la surface (dans le plan x-y) est definie´ par les coins opposes´ suivant la diagonale. Pour trouver ces coins, nous avons conc¸u un systeme` de coordonnees´ en 2-D. Les coins des cubes sont les intersections ses lignes de maillage perpendiculaires. Par exemple, le maillage de la figure 4a possede` les coordonnees´ sur l’axe X- X array = fa1; a2; a3; a4; a5; a6g et les coordonnees´ sur l’axe Y Yarray = fb1; b2; b3; b4; b5; b6g. Ces coordonnees´ sont la projec-tion sur les axes X et Y des sommets des masques DNTUB, et DPTUB. A titre d’exemple, les sommets de DNTUB produisent les coordonnees´ fa3; a4g pour l’ensemble X array et fb3; b4g pour l’ensemble Yarray.

Figure 5: Principe pour extraire un composant parasite. Les ronds rouges au centre des cubes deviendront les noeuds de la netlist resultante´.

d’el´ements´ en combinant plusieurs el´ements´. Pour pouvoir fusionner des petits el´ements,´ on doit respecter les 3 conditions suivantes: 1) memeˆ type de materiau;´ 2) l’el´ement´ fu-sionne´ realise´ une forme rectangulaire; 3) la forme resultante´ ne chevauche pas des sommets (rouges sur la figure). Par exemple, un groupe d’el´ements´ initiaux 1, 2, 3, 4, 5 (Cf. Figure 4a) recouvre les sommets (a2, b2) et (a5 b2), donc ils ne peuvent pas etreˆ fusionnes,´ memeˆ si ils sont composes´ du memeˆ type de materiau. Au contraire, le groupe d’el´ements´ initiaux 2, 3 (Cf. Figure 4a) peut etreˆ fusionne´ avec l’el´ement´ 4 sur la figure 4b. Cette technique de fusion reconstitue une structure unique de maillage composee´ de nouveaux el´ements´ de maillage de tailles distinctes.

Phase d’extraction

L’extraction des composants parasites du maillage produit une netlist. Cette netlist se compose de composants parasites avec des parametres` geom´etriques´. L’extraction d’un composant est ef-fectuee´ entre deux el´ements´ adjacents dans le maillage. Considerons´ deux el´ements´ adjacents du maillage, comme illustre´ sur la figure 5, un composant parasite est extrait entre leurs deux centres. En fonction des types de materiaux,´ le composant obtenu peut etreˆ soit une diode (si les materiaux´ sont de types differents),´ soit une resistance´ (memeˆ materiau),´ soit une homojonction (meme mais avec des concentrations de dopages differentes)´. Les parametres` geom´etriques´ ex-traits sont la longueur, surface, etc (Cf. tableau 3).

Outre la geom´etrie,´ on extrait egalement´ le materiau´. Par exemple, la resistance´ extraite du puits DNTUB differe` de celle extraite du puits DPTUB du fait de la nature du dopage du silicium, qui differe` egalement´ de la resistance´ extraite du substrat-P. Ceci entraˆıne des resistances´ extraites differenci´ees´ selon :

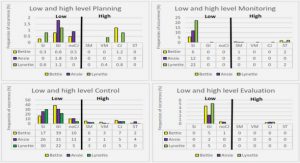

Notre premiere` etude´ de cas est la structure de ref´erence´ de la diode DNPS. Cette structure est une diode de dimensions 800µm x 800µm. Les parametres` de sortie provenant de l’extraction et de la simulation sont resum´es´ dans le tableau 5. Les resultats´ des comportements DC, y compris en polarisation directe et inverse sont present´es´ a` la figure 6. Les resultats´ respectifs des simulations sont dessines´ avec des lignes droites et les mesures avec des points. Dans la memeˆ figure, les courbes en couleurs montrent les comportements en fonction de la temperature´ : 27 C (bleu), 75 C (noir) et 125 C (rouge).

Figure 6: Comportements de la diode en fonction de la temperature´ en polarisation directe et inverse, a` 27 C (blau), 75 C (noir) et 125 C (rouge).

La modelisation´ du transistor parasite NPN lateral´ parasite est une tacheˆ difficile. Dans la tech-nologie CMOS HV, l’emetteur´ du transistor NPN est cause´ par l’injection, dans un caisson (puits)

N-well, d’un courant de substrat (gen´eralement´ issu d’un dispositif de puissance), les collecteurs sont les puits N-well environnants tandis que la base est la totalite´ du substrat de type P. Par consequent,´ l’extraction de ces dispositifs parasites suivant la geom´etrie´ du layout devient im-possible en utilisant le modele` BJT standard. Dans notre approche, la modelisation´ du transistor parasite NPN lateral´ s’appuie sur le maillage du substrat (Cf. Figure 7). Le maillage du sub-strat conduit a` modeliser´ le transistor parasite lateral´ NPN avec plusieurs diodes en fonction de la geom´etrie´ du layout. L’effet bipolaire parasite NPN est ensuite ajoute´ a` la netlist (post-layout) du circuit initial.

La deuxieme` structure de test et validation est un circuit fabrique´ par amsAG. Ce circuit de test contient 15 diodes DN-PS partageant le memeˆ substrat. Il dispose de plots d’entrees´-sorties. Les 15 premiers d’entre eux (PAD 1 a` 15) sont chacun connectes´ a` un des 15 puits N-well, et le dernier (PAD16) est connecte´ a` un anneau de P-well qui est le contact de substrat autour des 15 puits N-well. L’ensemble du circuit de test est extrait a` l’aide de notre methode´ (Cf. tableau 5). L’extraction de la totalite´ du circuit est realis´ee´ en deux etapes:´ 1) l’extraction des dispositifs parasites (chaque diode DN-PS); 2) l’extraction du substrat en dehors des zones occupees´ par les dispositifs. La structure du maillage est represent´ee´ a` la figure 8. Avant de proceder´ a` la simulation, il faut s’assurer que les 15 diodes DN-PS ne sont pas comptabilisees´ 2 fois (par l’extracteur du substrat et par l’extraction standard fondee´ sur le Process Design Kit du fondeur).

Figure 8: (a) Capture d’ecran´ de maillage de l’ensemble de la puce test; (b) la configuration des cas de test. (c) la carte en couleur de la chute de tension due a` l’injection de porteurs minoritaires.

Figure 9: Caracteristiques´ courant-tension du transistor parasite NPN lateral´ en fonction de la temperature´ : 25 C (bleu), 27 C (noir) et 125 C (rouge) et en fonction de la distance a` l’emetteur´ PAD5 (collecteur PAD1 au collecteur PAD4). Les courants a` l’emetteur´ (Ie) et au collecteur (Ic) sont present´es´ pour la simulation (lignes) et les mesures (symboles).

Dans le test que nous effectuons, present´e´ a` la figure 9, nous considerons` en particulier les plots PAD1 a` PAD5. Nous nous interessons´ principalement a` l’analyse des transistors parasites NPN lateraux´ et nous cherchons a` estimer l’effet de la distance. Chaque puits Nwell a la memeˆ dimension (20µm x 20µm), et est situe´ a` une distance differente´ de PAD 5. Pour la simulation, le plot PAD5 est la zone de substrat emettant´ et le collecteur est un des 4 autres plots, tandis que les 3 autres sont flottants. La comparaison avec les mesures montre un bon accord entre resultats´ de simulation et mesures (Cf. Figure 9), y compris avec la variation de temperature,´ ce qui confirme la validite´ de notre approche.

Dans la technologie CMOS HV, un caisson N profond isole les transistors du substrat de type P. Cette structure presente´ intrinsequement` un transistor parasite vertical a` jonction bipolaire NPN (cas d’un transistor N-MOS) ou PNP (cas d’un transistor P-MOS). Le drain du transistor P-MOS correspond a` l’emetteur´ du transistor parasite PNP vertical, qui est habituellement relie´ a` la charge. Les conditions de fonctionnement sont telles que le potentiel de ce drain peut etreˆ inferieur´ a` la tension la plus negative´ ou superieur´ a` la tension d’alimentation, au risque d’activer le transistor bipolaire vertical qui injecte alors du courant dans le substrat. Ce type de configuration se retrouve souvent dans les applications automobiles HV. En regle` gen´erale,´ le transistor vertical parasite peut etreˆ ajoute´ au modele` compact du modele` SPICE standard, cependant la propagation des courants de substrat est impossible a` modeliser´ avec cette approche, qui ne prend pas en compte l’ensemble du layout. Par consequent,´ dans notre approche, nous modelisons´ egalement´ les transistors para-sites verticaux par des combinaisons de diodes a` modele` enrichi.

Comparaison des resultats´ de simulation (lignes) aux donnees´ mesurees´ (symboles).

Dans la structure de test que nous avons etudi´ee´ prec´edemment,´ l’effet du transistor parasite NPN lateral´ etait´ produit en connectant des diodes laterales,´ entre des puits N-well, par leurs anodes. L’extraction des transistors parasites verticaux s’appuie, elle, sur differents´ puits N-well et P-well presents´ dans le substrat. Il faut donc prendre en compte divers types de diodes parasites en fonction de la jonction PN du puits consider´e´. La connexion entre les anodes de ces diodes propage des porteurs minoritaires permettant de simuler le comportement d’un transistor NPN parasite. D’une fac¸on analogue, la connexion de ces diodes par les cathodes permet de simuler le comportement d’un transistor PNP parasite.

Outre la diode DN-PS (jaune), on rencontre la diode DP-DN (bleu) et la diode ND-DP (verte) au cours de l’extraction du substrat (comme indique´ au tableau III). La calibration de ces diodes est realis´ee´ en utilisant les dispositifs bipolaires classiques de la bibliotheque` standard du fondeur qui definit´ precis´ement´ la geom´etrie´ de la structure BJT verticale (Cf. Figure 10). Les resultats´ concernant l’extraction et la simulation de deux transistors bipolaires sont present´es´ par le tableau IV. Il faut veiller a` ne pas prendre en compte 2 fois ces transistors verticaux (via la bibliotheque` de modeles` du fondeur et via notre extraction du substrat). Les caracteristiques´ courant-tension en DC obtenues par simulation sont represent´ees´ sur la figure 11 et validees´ par comparaison avec les mesures.

Les reseaux´ de substrat extraits dans les deux cas sont les memes,ˆ car ils representent´ la memeˆ geom´etrie´ du substrat (Cf. Figure 12c). Le circuit principal est retro´-annote´ avec la netlist extraite du substrat. Un signal transitoire sous forme d’impulsion negative´ (1V , 2µs) est applique´ comme source de tension d’entree´ (Cf. figure 13). Le potentiel negatif´ du drain du transistor M1 provoque l’injection de courant dans le substrat. Puis la polarisation, dans le sens direct, de la diode DN-PS parasite du transistor M1 declenche´ le transistor NPN lateral´. Par consequent,´ les courants des 3 transistors M1, M2 et M3 se trouvent couples´ par les puits DNTUB des transistors M2 et M3. Les courants de couplage dependent´ de la distance entre les dispositifs : IsubM2 > IsubM3, parce que dM1 M2 < dM1 M3. En consequence,´ la chute de tension au niveau du puits DNTUB du transistor M2 est superieure´ a` celle du transistor M3.

Dans le cas 1, le transistor M2 est la source du miroir de courant qui convertit le courant en tension. La chute de tension au drain de M2 (D2) provoque une baisse de tension a` la grille de M2. Du fait de cette chute de tension grille-source du miroir de courant, le courant de drain du transistor M3 diminue. Cette chute du courant recopie´ par le miroir n’est pas compensee´ par l’augmentation des courants de couplage a` travers le substrat, et donc le courant total du transistor M3 (Iout ) diminue. Au contraire, le courant total du transistor M2 (Ire f ) augmente car les courants dus a` la propagation a` travers le substrat y sont plus importants.

Dans le cas 2, le transistor M3 est la source du miroir de courant. Comme M3 est plus loin que M2 de l’agresseur, l’effet de couplage, a` travers le substrat, sur le miroir de courant est moindre que dans le cas prec´edent´ et la diminution du courant recopie´ par le miroir, est moins importante que l’effet de couplage des courants a` travers le substrat. Les courants de M2 (IOut ) et M3 (IRe f ) augmentent selon leur distance par rapport a` M1.

Le second cas de test est un circuit industriel fabrique´ par amsAG [41]. Son principe est present´e´ sur la figure 14. L’entree´ est un plot d’entree´-sortie (IO) qui se compose de deux diodes connectees´ en serie´ entre VDD et la masse. La source de l’agression se situe entre les deux diodes (Cf. ”Vin” Figure 14). Deux puits N-well de taille d4 d6 chacune, sont places´ pour collecter les charges injectees´. La distance a` l’emetteur´ est differente´ dans les deux cas et vaut respectivement d5 pour le plus proche et d5 +d6 +d7 pour l’autre. La sortie ”Vout ” est implement´ee´ par un plot. On utilise une option de decoupage´ au laser pour connecter ou deconnecter´ les differents´ puits N-well sur le plot ”Vout”.

Resume´ Etendu en Francais

Les resultats´ de cet essai sont present´es´ figure 15 lorsque la tension a` la sortie ”Vout ” est mesuree´ sur 50W. Les courbes sont affichees´ en fonction des differentes´ valeurs des tensions de crete:ˆ 6V, 12V et 20V. Les signaux provoques´ par le couplage a` travers le substrat ne peuvent pas etreˆ simules´ de maniere` classique. En utilisant notre outil, nous pouvons observer des signaux impulsionnels sur le puits correspondant (DN1 et DN2). Comme prevu,´ le signal simule´ est plus elev´e´ pour le signal d’entree´ de plus grande amplitude. Une distance plus courte a` la source de courant dans le substrat produit, comme prevu,´ un signal d’amplitude plus elev´ee´.

La modelisation´ des bruits de substrat est critique pour les circuits integr´es´ de puissance. Les bruits de couplage dans le substrat sont dus a` l’injection et a` la propagation des porteurs, partic-ulierement` en provenance des dispositifs haute tension. Les effets de ces porteurs sont amplifies´ a` haute temperature´. De tels bruits de couplage par le substrat ne sont pas previsibles´ a` l’aide d’une simulation SPICE standard qui ne propose pas de modele` compact du transistor parasite NPN lateral´ dans le substrat. Dans cette these,` nous avons present´e´ une methode´ d’extraction et simulation post-layout des parasites du substrat. Cette methode´ repose sur un outil de maillage du layout et de gen´eration´ de netlist de composants parasites pour representer´ le comportement du substrat. L’utilisation de notre outil complete` le flot existant de verification´ apres` le layout. Le comportement des courants de substrat peuvent alors etreˆ pris en compte dans la simulation post-layout. Nous avons extrait les parametres` technologiques du modele` de substrat pour diverses structures de ref´erence´ en technologie ams AG HV-CMOS 0:35µm. Nous avons etudi´e´ dans ce tra-vail l’effet du transistor bipolaire parasite NPN lateral´ dans deux cas de test : les perturbations par les courants de substrat d’un miroir de courant dans un premier cas, puis un cas de test standard pour une application automobile. L’approche proposee´ donne aux concepteurs la possibilite´ de simuler le comportement du substrat. La verification´ precoce´ du systeme,` avant fabrication, per-met de proteger´ le circuit conc¸u des effets du couplage par le substrat. Finalement, elle contribue a` reduire´ le cycle de conception et augmente ainsi la fiabilite´ et la securit´e´ des circuits integr´es´ intelligents de puissance.

Table of contents :

1 Introduction

1.1 Overview

1.2 Contribution

1.3 Outline

2 Motivation and Problem Definition

2.1 Introduction

2.2 Smart Power IC

2.2.1 Background

2.2.2 Description

2.3 Substrate Parasitic Interference

2.3.1 Basic physics

2.3.2 The Origin of Substrate Noise

2.3.2.1 H-bridge operation

2.3.2.2 Carriers Injection Due to Majority Carriers

2.3.2.3 Carriers Injection and Propagation Due to Minority Carriers

2.4 Motivations and European Project

2.4.1 Motivations

2.4.2 EU project: AUTOMICS

2.5 Conclusion

3 State of the Art in Substrate Parasitic Modeling

3.1 Introduction

3.2 State of the Art in Parasitic Modeling

3.2.1 Methodologies Using Substrate Parasitic R-C

3.2.2 Methodologies Using Substrate Parasitic BJT

3.2.3 Methodology Using Finite Element Device Simulation

3.3 EPFL Modeling Methodology

3.4 Conclusion

4 Methodology for Substrate Parasitic Extraction

4.1 Introduction

4.2 Computer-Aided-Design Framework

4.3 Layout-Based Extraction Methodology

4.3.1 Reduction Phase

4.3.2 Meshing Phase

4.3.2.1 Substrate Layering

4.3.2.2 2-D Surface Meshing

4.3.2.3 3-D Volume Meshing

4.3.3 Extraction Phase

4.4 Simulation and Evaluation

4.5 Conclusion

5 Mesh Refinement Strategy for Substrate Parasitic Extraction

5.1 Introduction

5.2 Mesh Refinement Strategy in Device

5.2.1 Mesh Refinement on 2-D Surface

5.2.2 Mesh Refinement in z-axis Direction

5.3 Mesh Refinement Strategy for Region

5.3.1 Descriptions of Design Structure

5.3.2 Applying Meshing Strategy for Regions

5.3.3 Simulation Results

5.4 Conclusion

6 Experimental Validation

6.1 Introduction

6.2 PDK Integration for HV-CMOS Technology

6.2.1 Identification of the Substrate PN Junction

6.2.2 Netlist Back Annotation

6.3 Model Benchmarking for HV-CMOS Technology

6.3.1 DNPS diode modeling

6.3.2 Parasitic lateral NPN modeling with DNPS diodes

6.3.2.1 Benchmark 1: impact of distance

6.3.2.2 Benchmark 2: impact of guard ring

6.3.2.3 Benchmark 3: impact of guard ring biasing

6.3.3 Parasitic vertical BJT modeling with enhanced diodes

6.4 Impact of Substrate Parasitic in HV-CMOS Technology

6.5 Industrial Test Evaluation in HV-CMOS Technology

6.6 Process Integration for BCD Technology

6.6.1 Silicon Structures Against Substrate Parasitic

6.6.2 Our Modeling Approach in BCD Technology

6.7 Model Benchmarking for BCD Technology

6.7.1 Benchmark 1: impact of the number of trenches

6.7.2 Benchmark 2: impact of shielding structures and trenches

6.8 Conclusion

7 Conclusion

7.1 Conclusion

7.2 Future Works