(Downloads - 0)

For more info about our services contact : help@bestpfe.com

Table of contents

1 Introduction

1.1 Background

1.2 Previous Work

1.3 Our Work

1.4 Research Contributions

1.5 Thesis Organisation

2 Resume (Francais)

2.1 Introduction

2.2 Radio logicielle

2.3 Test RF

2.3.1 Test et testabilite des systemes electroniques

2.3.2 Des dans le test des systemes RF

2.3.3 Etat de l’art du domaine de testabilite des systemes RF

2.3.4 Conclusions

2.4 Application de la technique de sous-echantillonnage non-uniforme au test integre des emetteurs RF exibles

2.4.1 Introduction

2.4.2 Outil theoriques

2.4.3 Description generale de l’architecture de test

2.4.4 Resultats en simulation

2.4.5 Conclusions et perspectives

3 Software Dened Radio

3.1 Introduction

3.2 Some History

3.3 What is an SDR

3.4 SDR Architectures

3.4.1 Receiver Architectures

3.4.2 Transmitter Architectures

3.4.3 State-of-Art SDR Transceiver Architectures

3.5 Transceiver Specications

3.5.1 Small-signal FoMs

3.5.2 Signal Power FoMs

3.5.3 Distortion FoMs

3.5.4 Noise Specications

3.5.5 Digital FoMs

3.5.6 Final Remarks on FoMs for RF Transceivers

3.6 Conclusions

4 RF Testing

4.1 Test and Testability of Electronic Systems

4.1.1 Test Classication

4.2 Challenges in AMS/RF Testing

4.3 Automated Test Equipments

4.4 Built-In Self-Test

4.4.1 Loopback BIST

4.4.2 Behavioral RF Modeling

4.4.3 Model-Based RF Test Strategies

4.4.4 Alternate Tests

4.5 Conclusions

5 Undersampling

5.1 Introduction

5.2 Nyquist Sampling

5.3 Bandpass Sampling Techniques

5.3.1 Classic Undersampling

5.3.2 Periodical Nonuniform Sampling of Second Order (PNS2)

5.3.3 Noise Degradation in Undersampling Techniques

5.4 Conclusions

6 SDR Test Strategy

6.1 Introduction

6.2 General Description of the Proposed Test Architecture

6.3 Digital PNS2 Reconstruction

6.3.1 FIR Implementation

6.3.2 Kaiser Window

6.3.3 Alternatives & Other Considerations

6.4 Delay Generation Block

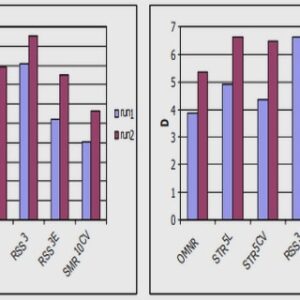

6.4.1 Choice of D

6.4.2 Reconstruction Robustness w.r.t. Uncertainties in D

6.4.3 DCDE Practical Implementation

6.4.4 Delay Estimation

6.5 Sample and Hold Elements

6.5.1 Charge-domain sampling

6.5.2 Improved BIST Architecture Based on CBS

6.6 Simulation Results

6.6.1 General Simulation Parameters

6.6.2 Adjacent Channel Power Ratio estimation

6.6.3 Digital PNS2 Reconstruction

6.6.4 Analysis of Time-Skew Detection Techniques

6.6.5 ACPR Simulation

6.7 Conclusions

7 Conclusions and Future Work

7.1 Conclusions

7.2 Future Work