Get Complete Project Material File(s) Now! »

Bit Interleaved Coded Modulation -BICM

First introduced by Zehavi in [8] and later on formalized by Caire et al: in [9], BICM offers an improvement in error correcting performance of coded modulations over fading channel. BICM is achieved by dispersing the coded binary data before mapping them to the modulated symbols. The idea is that bits related to one encoded symbol should be dispersed on different modulated symbols. By doing this bits from different coded symbols are affected by the fading effects and hence will increase the error correction capability of the decoder on the receiver side. This concept is explained with the help of Fig.1.5. In Fig. 1.5(a), bit interleaving is not applied on the bits of coded symbols (A, B, C, D, E). While passing through the channel one of the coded symbol (C) is completely destroyed. On the other hand, in Fig. 1.5(b), due to bit interleaving the bits of coded symbols are dispersed. Hence, with the same fading no single coded symbol is fully destroyed.

Quadrature Amplitude Modulation (QAM)

In this type of modulation the amplitude of two carriers (90o a part in phase) are changed in accor-dance with the incoming sequence of the digital data: S(t) = Accos2 fct Assin2 fct (1.11).

Here again we use the same two carrier signals as basic signals and Ac and As represent the coef-ficients of these two signals depending upon the different symbols in the modulation scheme. The constellation diagram of Gray mapped 16-QAM modulation is shown in Fig. 1.7.

Signal Space Diversity-SSD

SSD is a way of adding diversity in a modulated symbol before the transmission. Two low complexity solutions have been proposed in [10] to double the diversity order of Turbo BICM scheme (using turbo code and BICM in the transmitter). The proposed solutions are: correlating the in-phase I and quadrature Q component of the transmitted signal making these two components to fade independently

Correlating I and Q Components

When Gray mapping is used, QAM schemes are reduced to two independent Pulse Amplitude Mod-ulations (PAM) on every component axis represented by the I and Q channels. In Fig.1.7, bits v0 and v1 are mapped on I channel independently of bits v2 and v3 which are mapped on Q channel. Hence all constellation points cannot be uniquely identified in the I channel or Q channel separately.

In order to circumvent this natural independence and hope for any improvement in the diversity order, one should correlate the I and Q channels on every constellation point. This correlation has as purpose to uniquely identify every constellation point from any component axis. Since Gray mapping provides best performance with and without Iterative Demapping (ID) when turbo code is used [11], a simple solution to correlate both channels is to rotate the constellation as shown in Fig.1.8. This rotation does not change neither the distances between constellation points nor the distance to the origin hence no modification in transmission power or bandwidth is required.

Independent Fading of I and Q Components

When a transmitted constellation point is subject to a fading event, its I and Q coordinates fade identically. When subject to a destructive fading, the information transmitted on I and Q channels suffers from an irreversible loss leading to an erroneous detection of the symbol at the receiver side. If I and Q fade independently, in most cases it is highly unlikely to have severe fading on both components. One way to allow both components to fade independently has been proposed in [12]

Table of contents :

Dedication

Introduction

1 MultiWireless Standard Requirements and Turbo Reception

1.1 Wireless Communication System

1.2 Channel Models

1.2.1 Frequency Selectivity of a Channel

1.2.2 Time Selectivity of a Channel

1.3 Transmitter

1.3.1 Channel Coding

1.3.1.1 Convolutional Code

1.3.1.2 Convolutional Turbo Code

1.3.1.3 Multi Standard Channel Coding Parameters

1.3.2 Bit Interleaved Coded Modulation -BICM

1.3.3 Modulation/Mapping

1.3.3.1 Phase Shift Keying (PSK)

1.3.3.2 Quadrature Amplitude Modulation (QAM)

1.3.3.3 Multi Standard Mapper Specifications

1.3.4 Signal Space Diversity-SSD

1.3.4.1 Correlating I and Q Components

1.3.4.2 Independent Fading of I and Q Components

1.3.4.3 Multi Standard SSD Specifications

1.3.5 MIMO Space Time Code-STC

1.3.5.1 Diversity Techniques

1.3.5.2 Multiplexing Techniques

1.3.5.3 ST-BICM

1.3.5.4 MIMO-STC Specifications

1.3.6 Data Rate Requirements

1.4 Turbo Receiver

1.4.1 Turbo Decoding

1.4.2 Turbo Demodulation

1.4.3 Turbo Equalization

1.4.4 Unified Turbo Receiver

1.5 Conclusion

2 Turbo Reception Algorithms and Parallelism

2.1 Soft In Soft Out (SISO) Decoding Algorithm

2.1.1 MAP Decoding Algorithm

2.1.2 Log-MAP or max-log-MAP Decoding Algorithm

2.2 SISO Demapping Algorithm

2.2.1 Log Likelihood Ratio

2.2.2 Simplification of P(xt)

2.2.3 The max-log Approximation

2.2.4 Simplification For Gray Mapped Constellation

2.3 SISO Equalization Algorithm

2.3.1 MMSE-IC LE Algorithm

2.3.1.1 MMSE-IC1

2.3.1.2 MMSE-IC2

2.3.2 Soft Demapping

2.3.3 Soft Mapping

2.4 Parallelism in Turbo Receiver

2.4.1 Parallelism in Turbo Decoding

2.4.1.1 Metric Level Parallelism

2.4.1.2 SISO Decoder Level Parallelism

2.4.1.3 Parallelism of Turbo Decoder

2.4.2 Parallelism in Turbo Demodulation

2.4.2.1 Metric Level Parallelism

2.4.2.2 Demapper Component Level Parallelism

2.4.2.3 Turbo Demodulation Level Parallelism

2.4.3 Parallelism in Turbo Equalization

2.4.3.1 Symbol Estimation Level Parallelism

2.4.3.2 Equalizer Component Level Parallelism

2.4.3.3 Turbo Equalization Level Parallelism

2.5 Parallel System Modeling and Simulation Results

2.5.1 Parallel Turbo Demodulation

2.5.1.1 Software Model for Parallel Turbo Demodulation

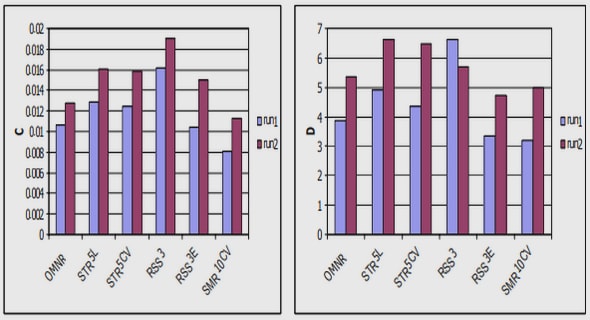

2.5.1.2 Simulation Results

2.5.2 Parallel Turbo Equalization

2.5.2.1 Software Model for Parallel Turbo Equalization

2.5.2.2 Simulation Results

2.6 Conclusion

3 Heterogeneous Multi-ASIP NoC-based Approach

3.1 Customizable Embedded Processors

3.2 ASIP Design

3.2.1 Design flow overview

3.2.2 CoWare’s ADL-based design tool: Processor Designer

3.3 NoC as communication interconnect

3.3.1 Emergence of InterIP-NoC

3.3.2 Network Topologies and Routing

3.3.3 NoC Examples in Iterative Decoding

3.4 Design Approach Illustration: Flexible Parallel Turbo Decoder

3.4.1 TurbASIP

3.4.1.1 Building Blocks of TurbASIP

3.4.1.2 Complete TurbASIP Architecture

3.4.1.3 Sample Program of TurbASIP

3.4.2 NoC Based on Butterfly Topology

3.5 Towards Heterogeneous Multi-ASIP and NoC Based Flexible Turbo Receiver

3.6 Conclusion

4 EquASIP: ASIP-based MMSE-IC Linear Equalizer

4.1 State of the Art

4.2 Flexibility Parameters and Architectural Choices

4.2.1 Flexibility Parameters

4.2.2 Architectural Choices

4.3 Hardware Architecture for Basic Operators

4.3.1 Complex Number Operations

4.3.1.1 Complex Number Addition, Subtraction, Negation and Conjugate

4.3.1.2 Complex Number Multiplication

4.3.1.3 Complex Number Inversion

4.3.2 Complex Matrix Operations

4.3.2.1 Matrix Hermitian, Addition, Subtraction, Negation

4.3.2.2 Matrix Multiplication

4.3.2.3 Matrix Inversion

4.3.2.4 Operator Reuse in Fixed-Point Representation

4.4 EquASIP Architecture

4.4.1 Matrix Register Banks

4.4.2 Complex Arithmetic Unit

4.4.3 Control Unit

4.5 EquASIP Instruction Set

4.5.1 LOAD, MOVE, REPEAT, NOP

4.5.2 Matrix Addition, Subtraction, Negation and Conjugation Instructions .

4.5.3 MULTIPLY

4.5.4 DIVIDE

4.6 Sample Program

4.6.1 Computation of E Matrix

4.6.2 2 2 Matrix Inversion

4.6.3 Computation of pj ; j ; j

4.6.4 Computation of pjj and gj

4.6.5 Symbol Estimation

4.7 EquASIP Results and Performance

4.7.1 Synthesis Results

4.7.2 Execution Performance

4.7.3 Comparison with State of the Art

4.8 Conclusion

5 DemASIP: ASIP-based Universal Demapper

5.1 State of the Art

5.2 Flexibility Parameters and Architectural Choices

5.2.1 Flexibility Parameters

5.2.2 Architectural Choices

5.3 Hardware Architecture for Basic Operators

5.3.1 Constellation Look Up Table (LUT)

5.3.2 Euclidean Distance Calculator

5.3.3 A priori Adder

5.3.4 Minimum Finders

5.4 DemASIP Architecture

5.4.1 Registers

5.4.2 Euclidean Unit

5.4.3 Control Unit (CU)

5.5 DemASIP Instruction Set

5.5.1 Configuration Control

5.5.2 Input

5.5.3 LLR Generation

5.5.4 Output

5.5.5 Loop

5.6 Sample Program

5.6.1 Inefficient Pipeline Usage Example

5.6.2 Efficient Pipeline Usage Example

5.7 DemASIP Results and Performance

5.7.1 Synthesis Results

5.7.2 Execution Performance

5.7.3 Comparison with State of the Art

5.8 Conclusion

6 Multi-ASIP NoC Based Turbo Receiver

6.1 ASIP Design, Validation and Prototyping Flow

6.1.1 LISA Abstraction Level

6.1.2 HDL Abstraction Level

6.1.3 FPGA Implementation Level

6.2 EquASIP and DemASIP FPGA Prototyping

6.2.1 EquASIP FPGA Prototype

6.2.2 DemASIP FPGA Prototype

6.3 First multi-ASIP Prototype: Parallel Turbo Decoder

6.3.1 Transmitter

6.3.1.1 Encoder

6.3.1.2 Combined Rate Control and BICM Interleaver

6.3.1.3 Parametrized Mapper

6.3.2 Rayleigh Fading Channel

6.3.3 Receiver

6.3.3.1 DemASIP Integration

6.3.3.2 BICM Deinterleaving and Depuncturing

6.3.3.3 multi-ASIP and NoC Based Turbo Decoder

6.3.4 Performance Results

6.4 Second multi-ASIP Prototype: Parallel Turbo Demodulator and Decoder

6.4.1 Transmitter

6.4.2 Receiver

6.4.2.1 Multi-ASIP Architecture for Parallel soft demapping

6.4.2.2 Modified TurbASIP Architecture

6.4.2.3 Communication Network Between TurbASIPs and DemASIPs

6.4.3 Performance Results

6.5 Third multi-ASIP Prototype: Parallel Unified Turbo Receiver

6.5.1 Transmitter

6.5.2 MIMO Flat Block Rayleigh Fading Channel

6.5.3 Receiver

6.5.3.1 MIMO equalizer

6.5.3.2 Soft Mapper

6.5.4 Performance Results

6.6 Conclusion

Conclusion and perspectives

Glossary

Bibliography